# **IIBLAST: Speeding Up Commercial FPGA Routing** by Decoupling and Mitigating the Intra-CLB Bottleneck

Shashwat Shrivastava, Stefan Nikolić, Chirag Ravishankar<sup>‡</sup>, Dinesh Gaitonde<sup>‡</sup>, and Mirjana Stojilović

<sup>‡</sup>AMD **EPFL**

1

3

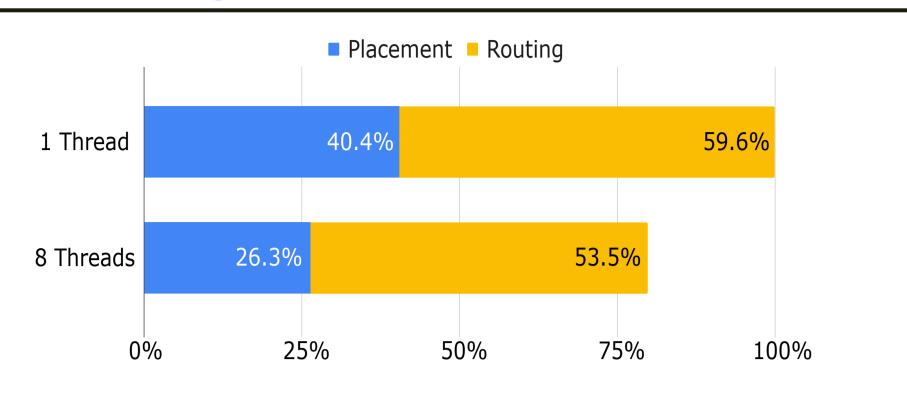

## Routing vs Placement Runtime

Routing is the major compilation bottleneck

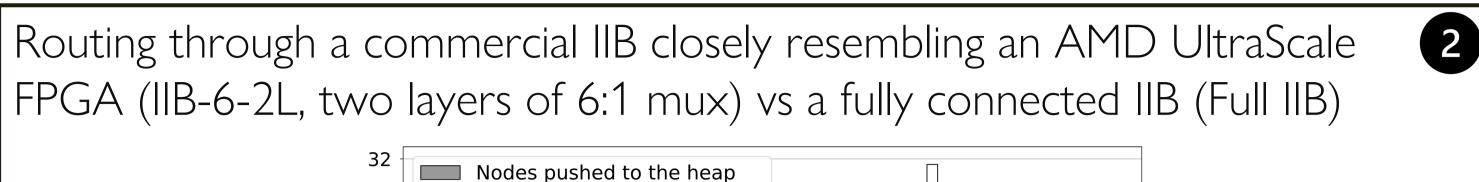

Impact of Commercial IIB

AMD

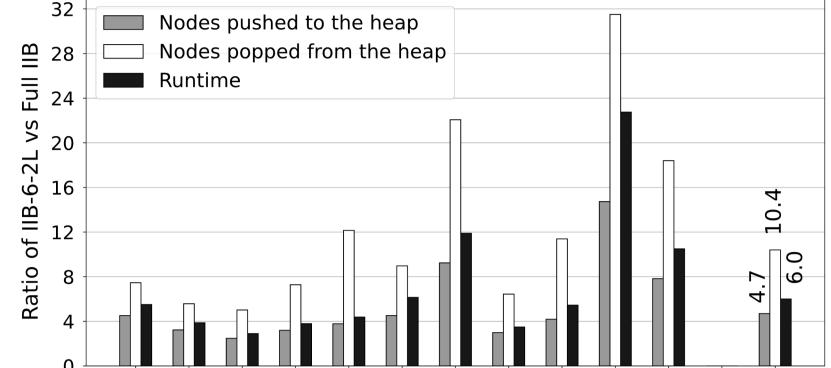

## Proposed Approach: Multi-Stage Router

#### 01 02 03 04 05 06 07 08 09 10 11 12 GM ISPD16 Benchmarks

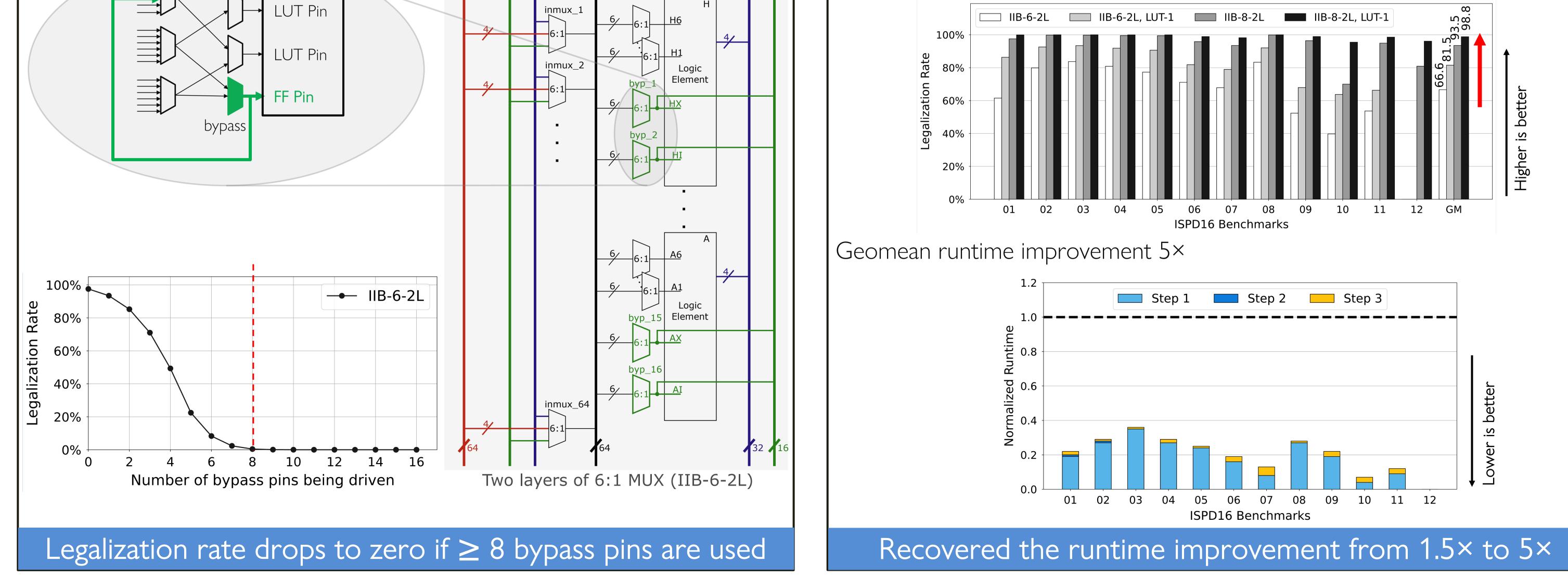

### Routing through commercial IIB is 6× slower

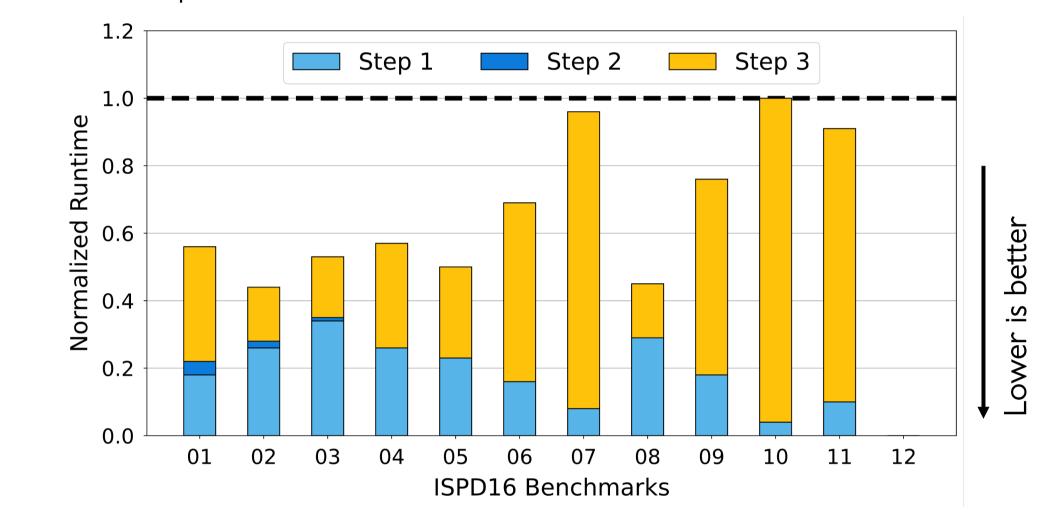

Multi-Stage Router vs Single-Stage Router

#### Geomean runtime improvement 1.5×

## Step 3 consumes significant fraction of runtime

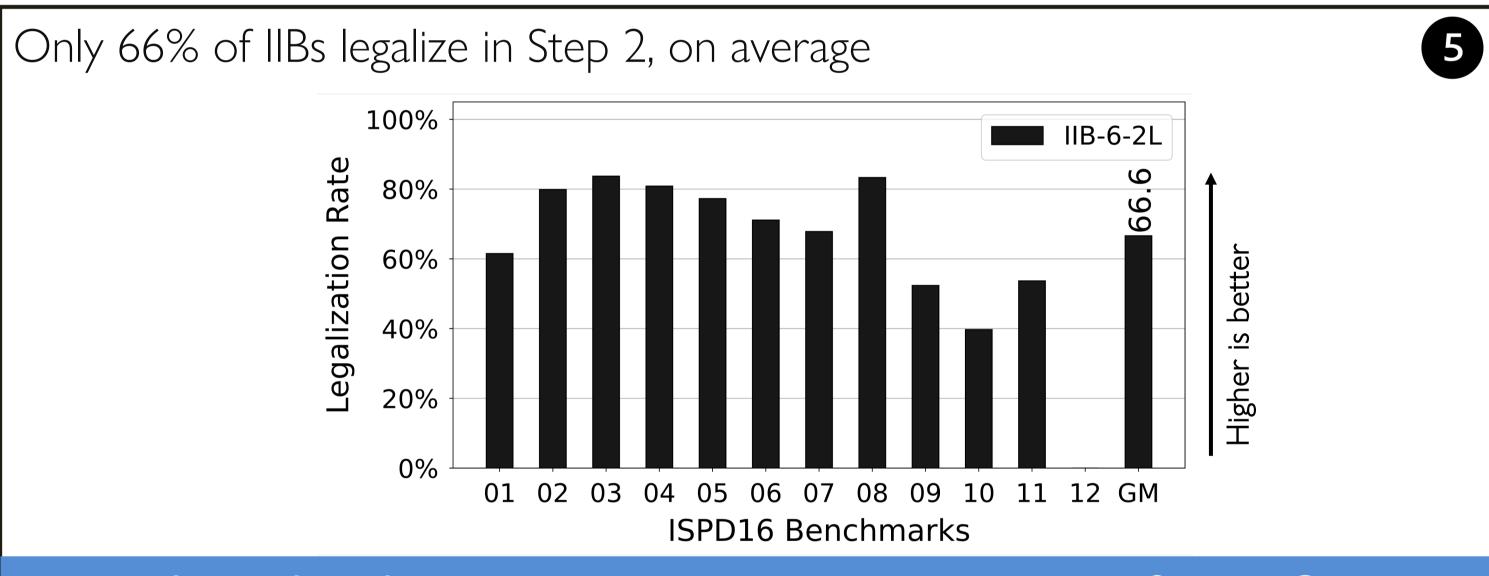

What is Increasing Step 3 Runtime?

#### Low legalization rate increases runtime of step 3

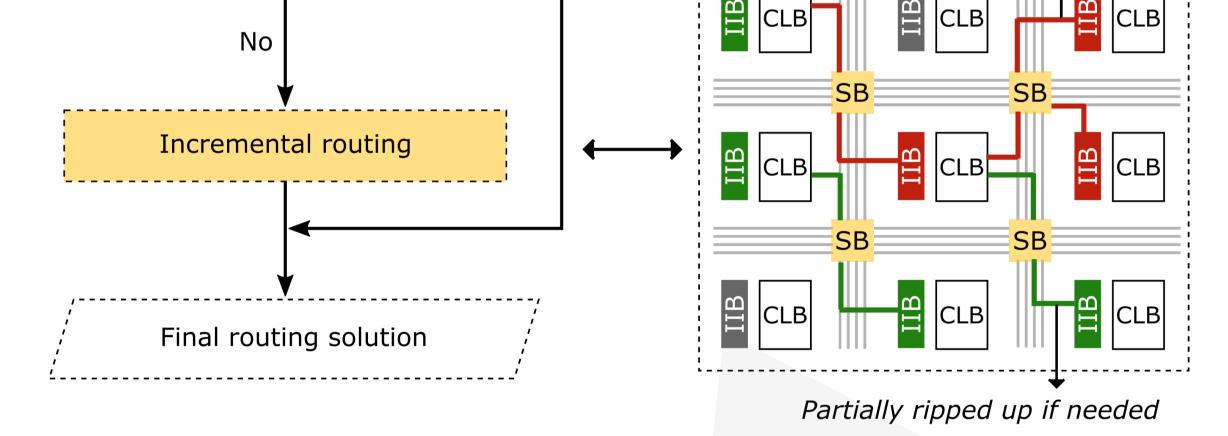

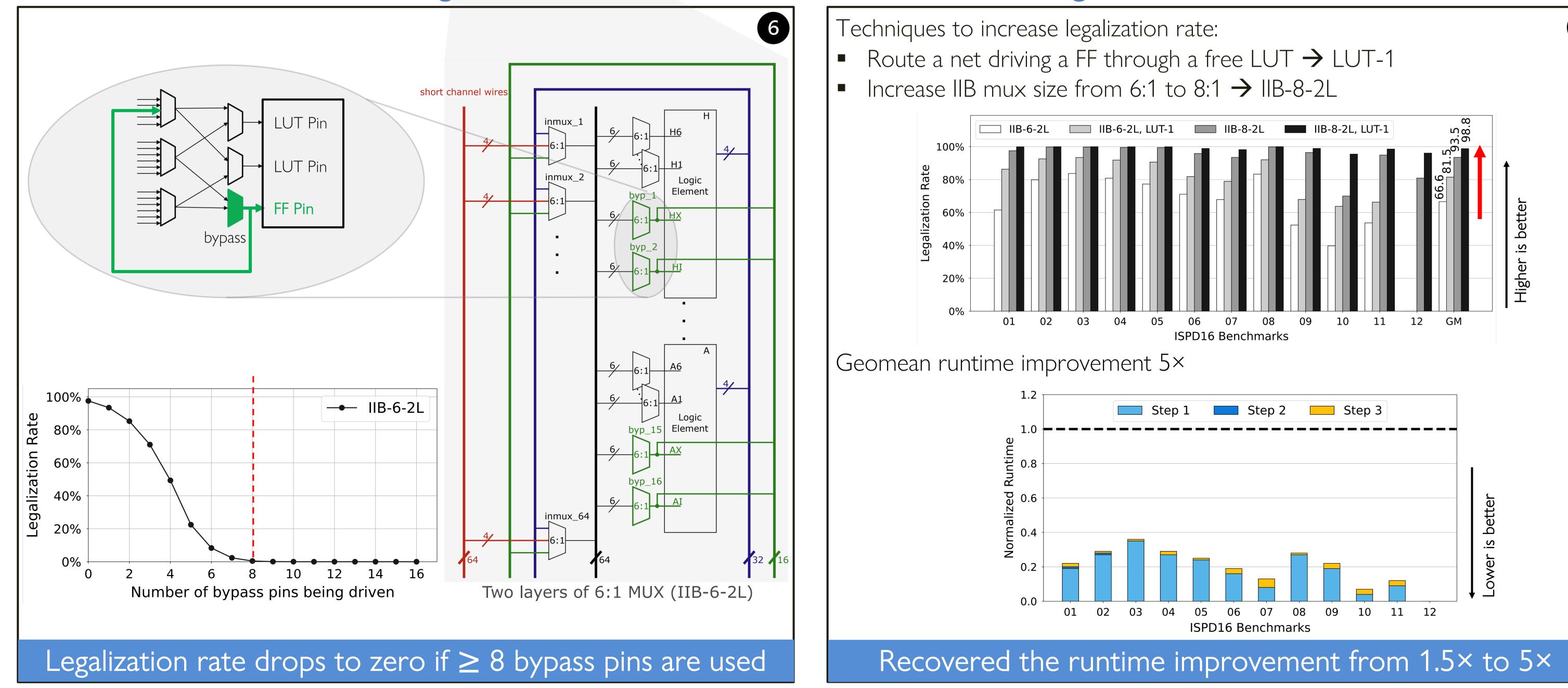

## Reason for Low Legalization Rate

## Multi-Stage Router with Enhancements

Our Multi-Stage Router coupled with architectural enhancements reduces runtime by 5×